# Revolt a Performance of IMD by Rectified Number of MLI Through Simulink Computational Method

<sup>1</sup>P.RAJAN, <sup>2</sup>P.RANJITH

<sup>2</sup>Lecturer of Electrical and Electronics Engineering Government polytechnic college, Arakandanallur,Villupuram. <sup>1</sup>Research Scholar, Christ College of Engineering and Technology, Pondicherry, INDIA

Abstract: Titled research work has been dealt with three different topologies of Multilevel Inverter. In the past decades, the researchers have dealt with the conventional topology one which possesses the twelve switches of Multilevel Inverter is applied to an Induction motor drive. The present research work has been introduced a new topology II system which reduces 10 and 5 switches in induction motor. The performance of the research work has been investigated through MATLAB simulation.

Keywords: Conventional Topology; Multilevel Inverter; Total Harmonics Distortion.

### **1. Introduction**

Nowadays, multilevel inverters have received more attention for their ability on high power and medium voltage operation and for other advantages such as high power quality, low order harmonics, lower switching losses and better electromagnetic interferences [1] These cascaded multilevel inverter generate a stepped voltage waveform, and more number of dc voltage waveform and switches will be used and they explain only the inverter operation and do not explain in application oriented. [2] These multilevel inverter are using a single phase seven level inverter for grid connected system. They are not implemented in induction motor, These cascaded h-bridge multilevel inverter generate a stepped waveform and more number of switches will be used and they explain only the single phase operation of multilevel inverter. They are not implemented in induction motor. [3] These symmetric multilevel inverter introduce the least number of switches, and gate trigger circuitry, switching loss are reduced, cost and size, but it is implemented in single phase circuit. [4] These cascaded multilevel inverter are using a nine and seven switches and sinusoidal pulse with (SPWM) technique modulation is also implemented using multicarrier wave signals, but they are not used in three phase circuit and used only in induction motor drive.[5]; [6]; [7]; [8];[9];[10]; [11]In recent years, different symmetric cascaded multilevel inverters have been presented, the main disadvantage of these circuits is some of them use a high number of bidirectional switches. More number of insulated gate bipolar transistors is required and they are not implemented in three phase circuit and induction motor drive.

Generally, voltage source inverter (VSI) and current sources inverter (CSI) are widely used for grid integration of renewable energy; recent trend goes towards the use of multilevel inverter. Because of these several benefits, MLI generates output having less distortion, produces lesser common mode voltage, produces less stress, reduces electromagnetic interference and generates better quality output.MLI also pertains to lesser and smaller filter size[12];[13].Several commercial MLI topologies are existing such as neutral point clamped inverter, flying capacitor, cascaded H bridge Among these, cascaded multilevel inverter is suited for induction motor drives application. In this paper, a new topology of multilevel inverter is proposed in order to increase the number of output voltage levels and reduce the number of switches, drives circuit, total cost of the inverter, and implementation of three phase circuit and induction motor drives. Moreover, the proposed topology is compared with other topologies from the different point of view. Such as number of IGBT, number of dc sources and performances of induction motor drives. Finally, the performances of the proposed topology in generating are voltage levels through a seven levels inverter is confirmed by simulation using a (MATLAB/SIMULINK).

## 2. Conventional Method

# 2.1 A 12 Switches Cascaded H-Bridge topology.

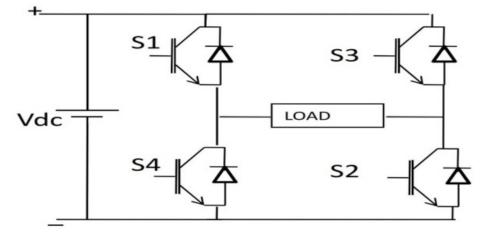

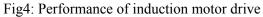

A single-phase structure of an m-level cascaded inverter is illustrated in Fig.1 . Each separate dc source (SDCS) is connected to a single-phase fullbridge, or H-bridge, inverter. Each inverter level can generate three different voltage outputs,  $+V_{dc}$ , 0, and  $-V_{dc}$  by connecting the dc source to the ac output by different combinations of the four switches, S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>, and S<sub>4</sub>. To obtain  $+V_{dc}$ , switches S<sub>1</sub> and S<sub>4</sub> are turned on, whereas  $-V_{dc}$  can be obtained by turning on switches S<sub>2</sub> and S<sub>3</sub>. By turning on S<sub>1</sub> and S<sub>2</sub> or S<sub>3</sub> and S<sub>4</sub>, the output voltage is 0. The ac outputs of each of the different full-bridge inverter levels are connected in series such that the synthesized voltage waveform is the sum of the inverter outputs. The number of output phase voltage levels m in a cascade inverter is defined by m = 2s + 1, where s is the number of separate dc sources. A stepped output voltage and current can be obtained in a cascaded MLI by cascading several H-bridge inverters. Adding another H-bridge to the existing H-bridge, number of levels increases by two. Hence for a 7-level output, three H-bridge inverters are to be cascaded as shown in Fig. 2. The switching states of the cascaded 7- level multilevel inverter are shown in Table1.Simulation results of output voltage waveform, THD and performance curve of induction motor and the content of conventional cascaded 7- level multilevel inverter respectively are shown in Fig.(3,4&5).

Fig:1 A single-phase structure of an m-level cascaded inverter

Fig2: Three phase cascaded multilevel inverter

Fig3: Output voltage of seven level inverter

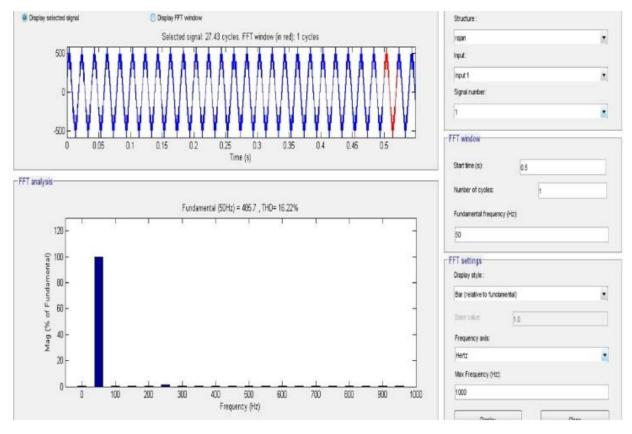

Fig5: FFT spectrum of seven level inverter

| Output<br>Voltage | S <sub>1</sub> | S <sub>1</sub> | S, | S4 | S; | S <sub>4</sub> | Sy | S <sub>2</sub> | S, | S <sub>10</sub> | S <sub>11</sub> | S <sub>L1</sub> |

|-------------------|----------------|----------------|----|----|----|----------------|----|----------------|----|-----------------|-----------------|-----------------|

| V.                | 1              | 0              | Q  | 1  | Û  | 0              | 1  | 1              | 0  | 0               | 1               | 1               |

| 2V.               | 1              | 0              | O  | 1  | 0  | 0              | 1  | 1              | 1  | 0               | 0               | 1               |

| 3V.               | 1              | 0              | O  | 1  | 1  | 0              | 0  | 1              | 1  | 0               | 0               | 1               |

| IV.               | 1              | 0              | 1  | 0  | 1  | 0              | 1  | 0              | 1  | 0               | 1               | O               |

| -V <sub>ik</sub>  | 0              | 1              | 1  | 0  | 1  | 1              | 0  | 0              | 1  | 1               | 0               | 0               |

| -2V.              | 0              | 1              | 1  | 0  | 0  | 1              | 1  | 0              | 1  | 1               | 0               | 0               |

| -3V.              | 0              | 1              | 1  | 0  | 0  | 1              | 1  | 0              | 0  | 1               | 1               | 0               |

Table1: Switching sequence of cascaded multilevel inverter using 12 switches

### **3. Induction motor model**

The dynamic model of an induction motor in the stationary reference frame can be written in dq frame variables. Stator voltage Vector  $V_s$  of the motor can be expressed as follows:

$$Vds = \left(d\psi * \frac{ds}{dt}\right) + (Rs * Ids)$$

(1)

$$Vqs = \left(d\psi * \frac{ds}{dt}\right) + (Rs * Iqs)$$

(2)

$$\psi s = \left(d\frac{\psi s}{dt}\right) + (Rs *$$

Is)

(3)

The stator flux vector  $\psi s$  and components can be written as:

$$\Psi ds = Ls * Ids + Lm * Idr$$

(4)

$$\Psi qs = Ls * Iqs + Lm * Iqr$$

(5)

$$\Psi s = Ls * Is + Lm * Ir$$

(6)

The rotor flux vector  $\psi r$  and components in the stator reference frame is

$$\psi dr = Lr * Idr + Lm * Ids$$

(7)

$$\psi qr = Lr * Iqr + Lm * Iqs$$

(8)

$$\psi r = Lr * Ir + Lm * Is$$

(9)

where *Vds* and *Vqs* are the stator voltages; *Ids* and *Iqs* are the stator currents; *Idr* and *Iqr* are the rotor currents;  $\Psi ds$  and  $\Psi qs$  are the stator fluxes;  $\Psi dr$  and  $\Psi qr$  are the rotor fluxes; *Is* and *Ir* are the stator and rotor currents vectors; *Rs* is the stator winding resistance., and *Ls*, *Lr*, *Lm* are stator, rotor self inductance and mutual inductance respectively. The electromagnetic torque *Te* is developed by the induction motor in terms of stator and rotor flux vectors *can* be expressed as:

$$Te = 3/2 * p(Lm/\sigma LsLr) \psi s * \psi r$$

$$Te = 3/2 * p(Lm/\sigma LsLr) |\psi s| *$$

$$|\psi r| \sin(\delta) \quad (10)$$

Where  $\sigma = 1 - (Lm^2/Ls * Lr)$  is the leakage factor; *p* is the number of pole pairs and  $\delta$  is the torque angle. From the above equation, it is clear that the electromagnetic torque is cross vector product between the stator and rotor flux vectors. Therefore, generally torque control can be performed by controlling torque angle  $\delta$  with constant amplitude of the stator and rotor fluxes.

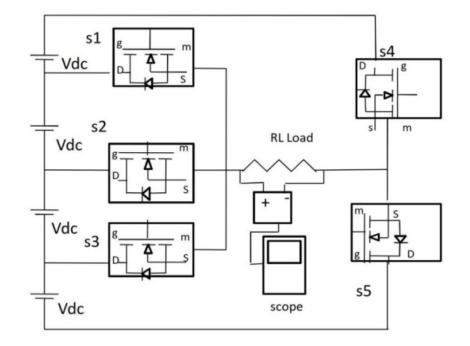

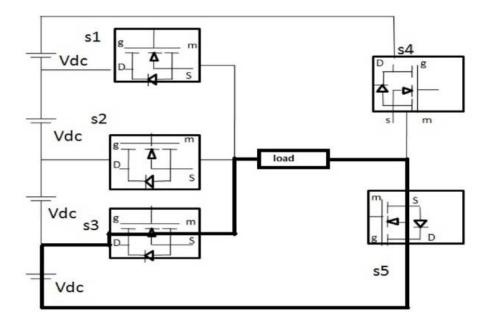

# 4. A 10 Switches multilevel inverter topology

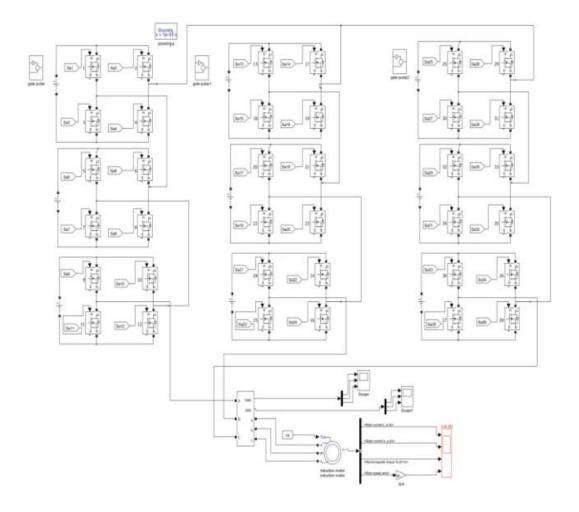

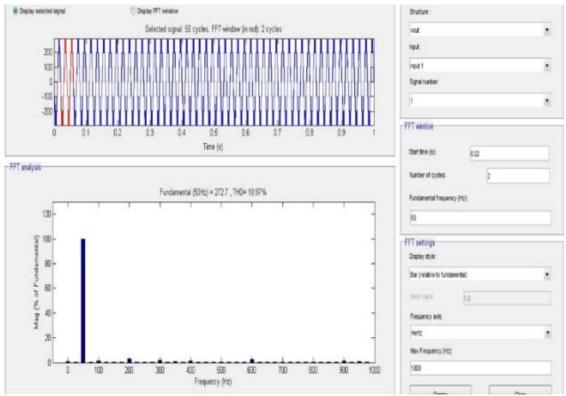

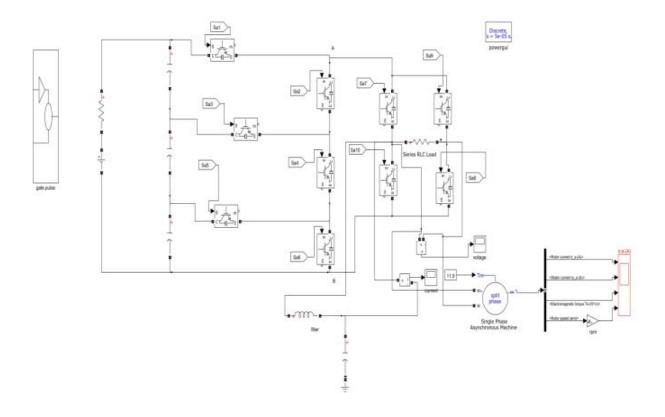

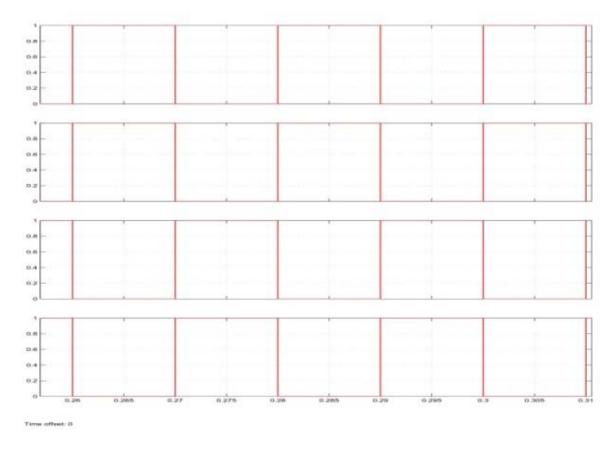

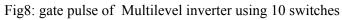

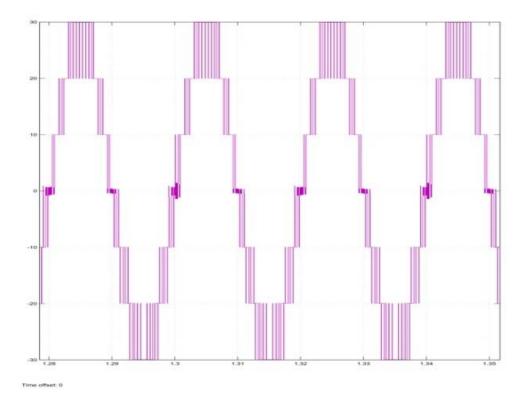

In conventional multilevel inverter, both positive and negative polarities in power switches are operated to produce a high frequency waveform. There is no need to use the switches to attain bipolar level. This basic structure of new proposed topology is shown in Fig 6. The power semiconductor switches in generation level is employed for polarity generation operating at the line frequency. The switching order for the generation of positive levels  $(0, V_{dc}/3, 2V_{dc}/3, V_{dc})$ are shown in Table 2. The required output voltage levels produced by the level generator are generated as follows; switches S<sub>2</sub>, S<sub>4</sub>, S<sub>6</sub> are ON which short circuit the input terminal AB of the polarity generation resulting in the generation of the zero. The current path that is active at this stage in zero output level. In one third positive output level, Switching S<sub>2</sub>, S<sub>4</sub>, S<sub>5</sub> are ON by connecting the terminal a to  $V_{dc}/3$  and terminal B to ground resulting in the generation of V<sub>dc</sub> at all other high frequency controlled switches. Switches S<sub>2</sub>, S<sub>3</sub> are ON and connecting the terminal A to  $2V_{dc}/3$  formed by the sum of two equal capacitor voltages and terminal B to ground in two-third positive output voltage. In maximum positive output level, S1 is ON and terminal A is connected to V<sub>dc</sub> and terminal B is ground resulting in generation of V<sub>dc</sub> In forward mode: switches S<sub>7</sub>&S<sub>8</sub> are ON, generating the positive polarity output. In reverse mode: switches S<sub>9</sub> & S<sub>10</sub> are ON, generating the negative polarity output. The gate pulse for MLI is shown in Fig.7& 8 respectively. The output voltage waveform & performance curve of induction motor are shown in Fig 9&10 respectively and the total

Fig6: Three phase Multilevel inverter using 10 switches

Fig7: Gate pulse of Multilevel inverter using 10 switches

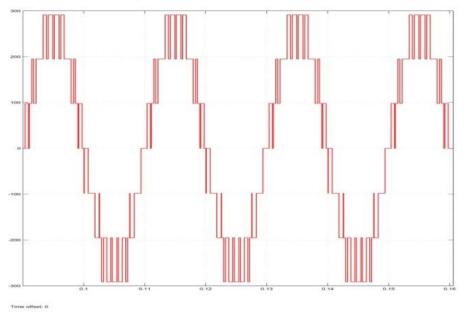

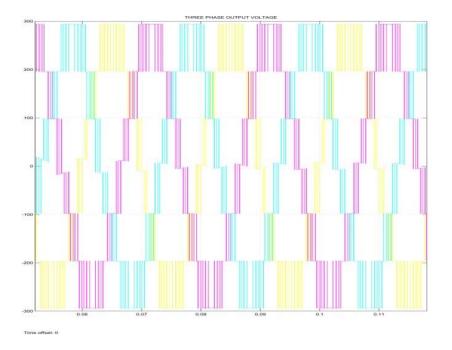

### Fig9: Output voltage of seven level inverter

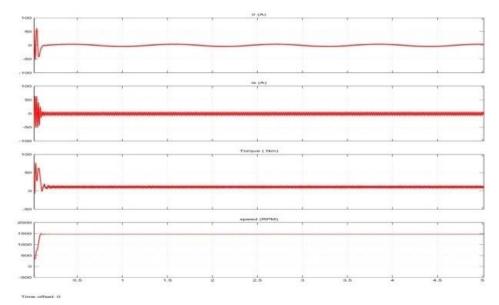

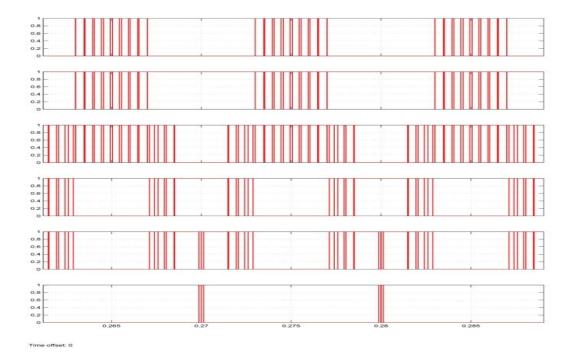

Fig10: Performance of induction motor drive

Fig11: FFT spectrum of seven level inverter voltage

| Output<br>Voltage | S <sub>1</sub> | S <sub>2</sub> | S3 | S4 | S <sub>5</sub> | S <sub>6</sub> | \$ <sub>7</sub> | Sg | Sg | S <sub>10</sub> |

|-------------------|----------------|----------------|----|----|----------------|----------------|-----------------|----|----|-----------------|

| Vdc/3             | 0              | 1              | 0  | 1  | 1              | 0              | 1               | 1  | 0  | 0               |

| 2Vdc/3            | 0              | 1              | 1  | 0  | 0              | 0              | 1               | 1  | 0  | 0               |

| Vdc               | Ĩ              | 0              | 0  | 0  | 0              | 0              | 1               | 1  | 0  | 0               |

| 0 Vdc             | 0              | 1              | 0  | 1  | 0              | 1              | 1               | 1  | 0  | 0               |

| -Vdc/3            | 0              | 1              | 0  | 1  | 1              | 0              | 0               | 0  | 1  | 1               |

| -2Vdc/3           | 0              | 1              | 1  | 0  | 0              | 0              | 0               | 0  | 1  | 1               |

| -Vdc              | 1              | 0              | 0  | 0  | 0              | 0              | 0               | 0  | 1  | 1               |

Table2: Switching sequence of multilevel

inverter using 10 switches

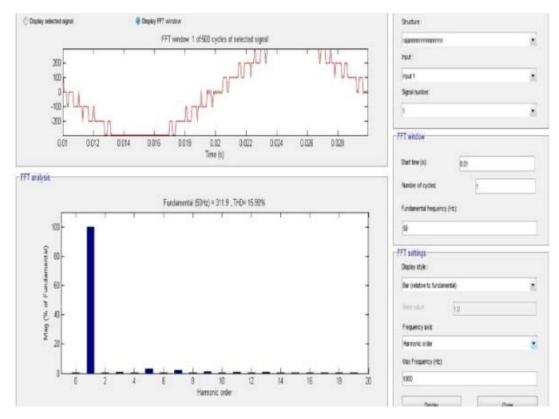

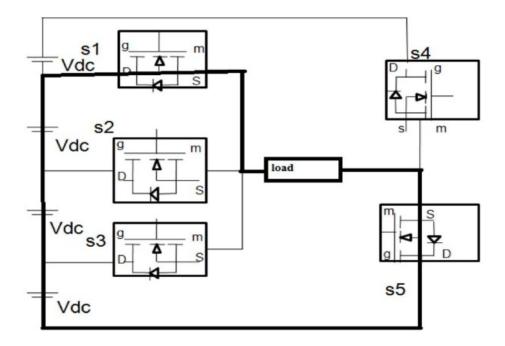

# 5. A 5 switches multilevel inverter topology

#### 5.1 .Circuit Description

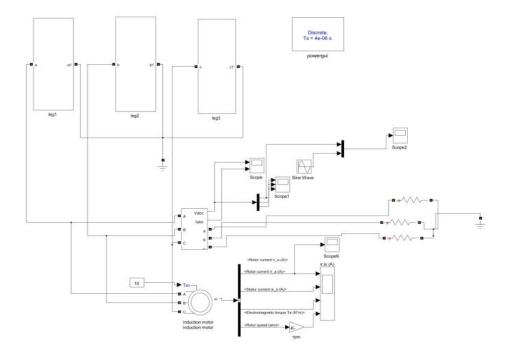

The proposed five switched topology has been introduced in Fig.12. The Fig.13 shows the simulation of three phase circuit of proposed topology. It is about modifying or reducing single switch from 10 switches topology obtaining the tag of 5 switches configuration. The proposed 5 switches topology is simpler design compared to all conventional topologies. This proposed topology method using generalized expression for the output voltage level is

$$V_0 = (2 * S_n - 3)$$

Where  $V_0 =$  Number of output voltage level

$S_n$  = Number of switches

$$V_0 = (2 * V - 1)$$

Where V = Number of DC sources

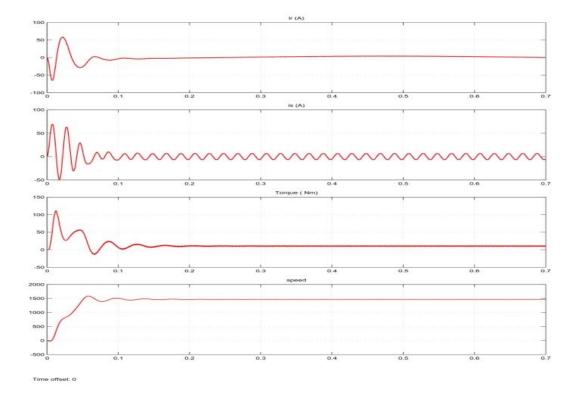

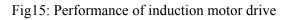

To obtain the unique pulse pattern and trigger the switches at the proper instant, switches  $S_1$ ,  $S_2$ and  $S_3$  get compulsorily unidirectional, otherwise the output waveform will get distorted. The system is more compact anduser friendly by using reduced number of switches. The seven levels MLI result in less utilization of sources through the usage of the four separate dc sources for the generation. Number of H-Bridge is used and it plays 2 switches producing reversal polarity. Table.3 represents the switching scheme for the proposed topology. The output voltage waveform & performance curve of induction motor is shown in Fig 14&15 respectively and the total harmonic output is noted in Fig.16.

Fig12: Proposed multilevel inverter using 5 switches

Fig13: Three phase multilevel inverter using 5 switches

Fig14: Output voltage of seven level inverter

Fig16: FFT spectrum of seven level inverter voltage

| Output Voltage     | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S4 | S <sub>5</sub> |

|--------------------|----------------|----------------|----------------|----|----------------|

| V <sub>dc</sub>    | 0              | 0              | 1              | 0  | 1              |

| 2 V <sub>dc</sub>  | 0              | 1              | 0              | 0  | 1              |

| 3 V <sub>de</sub>  | 1              | 0              | 0              | 0  | I              |

| 0 V <sub>dc</sub>  | 0              | 0              | 0              | 0  | 0              |

| -V <sub>dc</sub>   | 1              | 0              | 0              | 1  | 0              |

| -2V <sub>dc</sub>  | 0              | 1              | 0              | 1  | 0              |

| -3 V <sub>dc</sub> | 0              | 0              | 1              | 1  | 0              |

Table3: Switching sequence of multilevel inverter using 5 switches

Fig17: Switching sequence required to generate output voltage level  $V_{dc}$

Fig18: Switching sequence required to generate output voltage level  $2V_{dc}$

Fig19: Switching sequence required to generate output voltage level 3Vdc

| Multilevel inverter Type | Cascaded 12 Multilevel<br>Inverter | 10 switches multilevel<br>inverter | 5 switches multilevel<br>inverter |  |  |

|--------------------------|------------------------------------|------------------------------------|-----------------------------------|--|--|

| Main Switches            | 12                                 | 10                                 | 5                                 |  |  |

| Capacitor                |                                    | 3                                  |                                   |  |  |

| Voltage Sources          | 3                                  | 1                                  | 4                                 |  |  |

| THD ( % )                | 19.97                              | 16.22                              | 15.98                             |  |  |

Table4: Comparative evolution of multilevel inverter.

### 5.2. Power Stage Operation

The switching sequences for the generation of positive levels (0,  $V_{dc}$ ,  $2V_{dc}$ ,  $V_{dc}$ ) named as level 0, level 1, level 2, level 3 are as shown in Table 3. According to the table, there are four possible switching states to control the inverter. The required output positive voltage levels produced by the level generator are generated as follows:

1) Zero output level:  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ ,  $S_5$  are OFF in the generation of zero voltage (0 level) is shown in Table 3.

2)  $V_{dc}$  output voltage level:  $S_3,S_5$  are ON. All the other switches are OFF resulting in the generation of 1  $v_{dc}$ . Fig.17 shows the current paths that are active at this stage.

3)  $2V_{dc}$  output voltage level:  $S_2, S_5$  are ON. All the other switches are OFF resulting in the generation of  $2v_{dc}$ . Fig.18 shows the current paths that are active at this stage.

4)  $3V_{dc}$  output voltage level:  $S_1, S_5$  are ON. All the other switches are OFF resulting in the generation of  $3V_{dc}$ . Fig. 19 shows the current paths that are active at this stage.

## 5. comparative Evaluation

In order to clarify the advantages and disadvantages of the proposed topology, it should be compared with the different kinds of topologies presented in this paper. In the comparison the number of switches, DC bus capacitor, Voltage sources and THD are taken and tabulated in Table.4.

### 6. Conclusion

In this paper, a new topology with 10 switches and 5 switches is introduced and the same 7-level output is observed in either of the cases and shows the performance result of induction motor. Circuits are simulated using MATLAB/SIMULINK software total and harmonic distortions are obtained. It can be seen that the 5-switch topology is better than other presented topology because it requires a lesser number of switch and also THD content is lower in comparison with other mentioned topology.

#### References

[1] Ebrahim Babaei, "A New General Topology for Cascaded Multilevel Inverters With Reduced Number of Components Based on Developed H-Bridge", IEEE Transactions Industrial Electronics, Vol. 61, No. 8, August 2014.

[2] Prachi Salodkar, "A New Simplified Multilevel Inverter Topology for Grid-Connected Application", 2014 IEEE Students' Conference on Electrical, Electronics and Computer Science. 978-1-4799-2526-1/14/\$31.00 ©2014 IEEE.

[3] S.Umasankar, "A New 7-Level Symmetric Multilevel Inverter with Minimum Number of Switches", Hindawi Publishing Corporation ISRN Electronics Volume 2013, Article ID 476876.

[4] D P.Kothari, "Cascaded Seven Level Inverter With Reduced Number Of Switches Using Level Shifting PWM Technique", 2013 International conference on power, energy and control (ICPEC).pp 676-679.

[5] Y.Hinago and H. Koizumi, "A singlephase multilevel inverter using switched series/parallel dc voltage sources," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2643–2650, Aug. 2010.

[6] G. Waltrich and I. Barbi, "Three-phase cascaded multilevel inverter using power cells with two inverter legs in series," IEEE Trans. Ind. Appl.,vol. 57, no. 8, pp. 2605–2612, Aug. 2010.

[7] W. K. Choi and F. S. Kang, "H-bridge based multilevel inverter using PWM switching function," in Proc. INTELEC, 2009, pp. 1–5.

[8] E. Babaei, M. Farhadi Kangarlu, and F. Najaty Mazgar, "Symmetric and asymmetric multilevel inverter topologies with reduced switching devices," Elect. Power Syst. Res., vol. 86, pp. 122–130, May 2012.

[9] J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A new multilevel converter topology with reduced number of power electronic components," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp. 655–667, Feb. 2012.

[10] E. Babaei, S. H. Hosseini, G. B. Gharehpetian, M. Tarafdar Haque, and M. Sabahi, "Reduction of DC voltage sources and switches in asymmetrical multilevel converters using a novel topology," Elect. Power Syst. Res., vol. 77, no. 8, pp. 1073–1085, Jun. 2007.

[11] E. Babaei and S. H. Hosseini, "New cascaded multilevel inverter topology with

minimum number of switches," Energy Convers. Manage., vol. 50, no. 11, pp. 2761–2767, Nov. 2009.

[12] S.Daher, J.Schmid, and F.L.M. Antnus, "Multilevel Inverter Topologies For Stand Alone P.V System", IEEE trans.ind.electronics.,vol.55,no.7,pp,2703-2712,july 2008.

[13] J.Rodriguez, J.Lai, And F.Z.Peng, "Multilevel Inverters: A Survey Of Topologies, Controls and Application", IEEE Transactions On Industrial Electronics, Vol. 49, No. 4, August 2002.